Information Exchange for Your Application & Use of Cost Modeling

Since 1991

Volume 18. Issue 2

COO for c-Si Wet Processes: Texturization and Cleaning, Part 1 ......1

Calendar of Events.....2

WWK Conducts 6th Annual Semiconductor Manufacturing Technology Survey......10

WWK Hosts COO Seminar at SEMICON West / Intersolar .....11

WWK Launches LCOE Modeling Platform ......12

Upcoming "Modeling 101" Paper in Future PV......13

WWK to Present at the PV Fab Managers Forum Europe......13

### Cost of Ownership for c-Si Wet Processes: Texturization and Cleaning

With this edition of Applied Cost Modeling, we are publishing the first installment in a series on the application of cost of ownership (COO) and overall equipment efficiency (OEE) to crystal silicon-based (c-Si) photovoltaic (PV) texturization and cleaning.

#### Introduction<sup>1</sup>

This paper examines the need for saw damage removal and the follow-on processes of precleaning, texturization and cleaning. We further discuss the process considerations for wet and plasma approaches before taking a detailed look at texturization using random pyramid formation. The paper will conclude with a view of current and future wet process techniques and a COO case study using the Akrion Systems GAMA-Solar as an example.

## The Need for Saw Damage Removal, Precleaning, Texturization and Cleaning

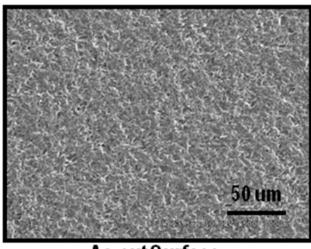

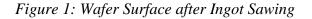

In practice, there are four operations that are performed as part of the surface conditioning process in cell manufacturing. These are saw damage removal, precleaning, texturization and cleaning. Saw damage results from the wire sawing process used to slice silicon ingots into wafers. As a result of this mechanical process, cracks of about 1-10  $\mu$ m deep are introduced into the surfaces of the wafer (see figure 1). Removing the saw damage from the wafer surface improves the mechanical strength of these thin wafers and increases the recombination at the surface region.

*First published in Photovoltaics International, 7<sup>th</sup> edition.* [Continued on page 3]

## Editorial Board

Dr. Scott Mason Fluor Endowed Chair in Supply Chain Optimization & Logistics Clemson University

Dr. Frank Chance President FabTime, Inc.

Dr. Vallabh H. Dhudshia Author Hi-Tech Equipment Reliability

Mr. Michael Wright Principal Applied Global Strategies, LLC

Mr. David L. Bouldin Principal Fab Consulting

Published quarterly by:

Wright Williams & Kelly, Inc. 6200 Stoneridge Mall Road 3<sup>rd</sup> Floor Pleasanton, CA 94588

Phone

925-399-6246

Fax

925-396-6174

E-mail

support@wwk.com

Available at: http://www.wwk.com Select "Newsletter"

# Calendar of Events

## March 2012

- 19-21 PV America West San Jose Convention Center San Jose, CA

- 20-22 SEMICON/FPD China New International Expo Center Shanghai, China

- 25-27 PV Fab Managers Forum Europe Hotel Kempinski Bristol Berlin, Germany

- 27 WWK COO Presentation PV Fab Managers Forum Europe

## April 2012

2-5 North American Standards Meeting SEMI Headquarters San Jose, CA

## Мау 2012

15-17 Advanced Semiconductor Mfg. Conference Saratoga Hilton Saratoga Springs, NY

## June 2012

13-15 Intersolar Europe New Munich Trade Fair Centre Munich, Germany

APPLIED Cost MODELING Winter 2012

As-cutSurface

Precleaning removes surface contaminants on the wafer that can lead to differences in texturization features sizes. These differences have a direct effect on surface reflectance.

Texturization is a light trapping technique which increases light absorption, which in turn, increases energy production over a given surface area. Increases in light absorption can be accomplished through a variety of texturization techniques and/or through the application of antireflective coatings (ARC).

Cleaning is the removal of metal, particulate, and organic contamination. These contaminants can negatively impact the performance of the solar cell; short-term or long-term. Ultraclean wafers are critical for obtaining high yields in the solar cell fabrication process.

#### Saw Damage Removal

Saw damage induced at the wafer sawing level (see figure 1) can be removed with either wet alkaline or acidic solutions. These solutions etch the top layer of silicon. Dry damage removal by plasma etching is

also possible. The saw damage removal step can be combined in the same equipment with the texturization step (see figure 2).

#### Precleaning

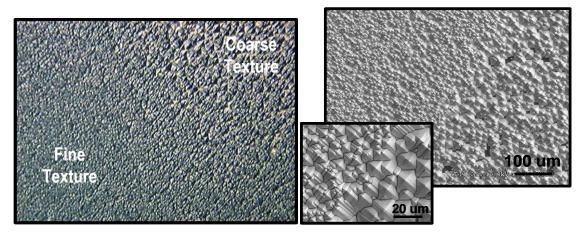

Examinations of surface morphology indicate that reflectance variations are associated with the lack of homogeneity of texture features as shown in figure 3a. Further analysis by scanning electron microscope (SEM) shows that this results from an abrupt change in pyramid sizes from one area to another (figure 3b). The area of low reflectance was found to correspond to the area of small pyramids. The texturization inconsistency appears to be due to surface contamination on the This can be demonstrated by wafers. intentionally touching a precleaned wafer with a cleanroom glove and noting the dark patterns at the corresponding areas after texturization.

#### **Texturization**

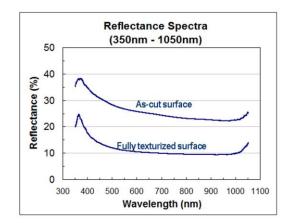

Light management in the solar cell is critical. Silicon, a material with an indirect band gap, has a relatively low absorption coefficient. Efficient surface texturization, coupled with an ARC (see figure 4), can reduce reflectance losses from 35% to below  $10\%^{2}$ . <sup>3</sup>. As shown, a well

Figure 2: Integrated Saw Damage Removal, Precleaning, Texturization, and Cleaning Equipment

Figure 3: Surface Morphology of an Inconsistently Textured Area; (a) Optical Microscopy Image and (b) SEM Image

APPLIED Cost MODELING Winter 2012 5

texturized surface reflects only 9.5% at 950 nm compared to greater than 20% reflectance for an as-cut (untreated) surface.

*Figure 4: Reflectance with and without Texturization*

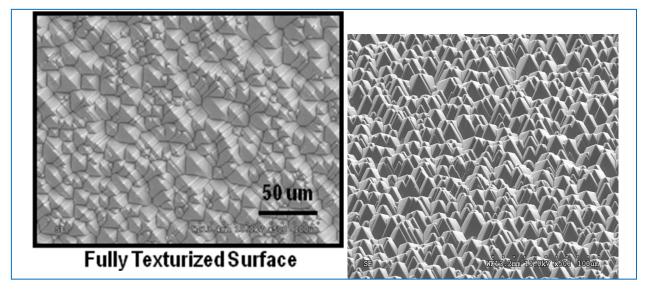

<100> orientation. An alkaline etchant exhibits an etch rate approximately 100 times faster along <100> than along <111>and, hence, the <111> facets are developed. These facets are formed at 54.7 degrees to the horizontal plane. This result is the formation of small pyramids with a square base, randomly distributed over the wafer surface (see figure 5).

The degree of anisotropy (i.e., etch rate selectivity between different crystal planes), the etch rate, and homogeneity depend on the etching temperature, chemical concentration, and bath impurities. An additional factor to consider is that the typical etch bath creates residual etch by-

Figure 5: Random Pyramid Structures

The bonding energy of silicon atoms is different for each crystal plane. This turns out to be very useful. Alkaline etching is not diffusion limited, instead it is driven by the differences in etch rate for the crystal planes. The result is that silicon etching is highly anisotropic. This mechanism is well understood. The <111> plane is more densely packed than the <100> plane and, thus, the etch rate of the <111> oriented surfaces are much less than those in the products. These silicates act as seeds (or nuclei) that initiate the pyramid formation and also act as an etch mask (or micromask) at that location. However, once these silica seeds exceed a critical concentration, they act as a contaminant, suppressing the etch rate sufficiently that the bath will no longer be effective in creating the random pyramid structures.

#### Cleaning

After texturization, the wafers are rinsed with deionized (DI) water, cleaned in HF

and/or HCl to remove metal impurities on the wafer surface, and then dried in hot gas (e.g., heated clean dry air [CDA] or nitrogen). HCl removes surface impurities while HF removes the native oxide and any embedded impurities in the oxide, leaving the wafer surface nearly free of trace metals<sup>4</sup>. This results in an increased minority carrier A metal level of  $<5x10^{10}$ life time. atoms/cm<sup>2</sup> could be obtained for Al, Cu, Fe, Mg, Mn, and Zn with this  $clean^4$ . This results in an increased minority carrier life time and improved sheet resistance. This HF-last process renders the surface Hterminated and is highly desirable prior to high temperature phosphorous diffusion.

#### Process Choices: Wet vs. Plasma

The common chemicals used to do the texturization are mixtures of KOH/IPA or NaOH/IPA. The IPA is a wetting agent to improve the lateral uniformity and anisotropy of the etching process. Alkaline concentration can vary from 2-5% to 10-20% by weight. Process temperatures can vary from 70-90 degrees C. Process time can vary from a few minutes to an hour depending on the desired results.

With increasing price pressure and COO concerns, equipment can be specified to produce in excess of 3000 wafers/hour (wph). Equipment is typically configured with multiple baths for the same chemistry and batch sizes of 200 wafers. Wafers are held in cassettes and moved automatically from bath to bath. Wafers are typically exposed to this harsh chemistry for 30 minutes to produce these random pyramids. In-line processing has met with limited interest due to the length of the equipment needed to support long process times.

It is worth noting that wet processes dominate the manufacturing base. There is extensive learning that has been applied to

wet processing, allowing for high quality, reliable, and productive equipment. The materials themselves are readily available at high purity levels. While some might suggest this is a 'mature' process and thus has limited remaining upside, nothing could be further from the truth. In practice, it is this depth of understanding that allows for improvements to be made on a rapid basis. That's why immersion batch equipment like incorporated GAMA-Solar have the following features:

- Advanced process control (APC) using concentration sensors; ensuring repeatability, robustness and equipment uptime needed for volume manufacturing.

- Low defects using advanced drying techniques leaving no streaks on the wafers. Ultrasonics/megasonics are often employed to further reduce defects in process and rinse tanks.

- Etch and texturization uniformity across the wafer, within wafers, and lot-to-lot by optimizing tank design for more uniform fluid flow.

- Equipment reliability and flexibility by using modular designs that offer better control on water and chemical usage, exhaust volumes, and future upgradeability.

- Smaller footprint

- All of the above having a positive impact on COO

Plasma processes are a relatively recent entrant into texturization. Plasma processes have certain advantageous attributes when compared to wet processing. These include reduced handling, reduced waste disposal and reduced consumption of wet chemicals, including DI water. In addition, since plasma etching is single-sided, it creates new possibilities for treating the backside of the wafer. These possibilities include the

APPLIED Cost MODELING Winter 2012 use of multicrystalline materials without saw damage, such as edge-defined, film-fed growth (EFG), which cannot be processed using common chemical bath texturization methods.

A distinction has to be made between reactive ion etching (RIE) and other types of plasma texturization. RIE relies on the ion bombardment texturization, which results in a formation of so-called 'black silicon' and creates surface and subsurface damage that has to be removed for further cell processing (e.g., dopant diffusion).

RIE process chemistry is based on  $SF_6/O_2$  or Cl<sub>2</sub>. This technique has been proven to yield low reflectance with good uniformity, resulting in superior response in the long wavelength region. However, the defects induced by the ion bombardment can severely degrade the internal quantum efficiency (IQE). A possible solution is to use a damage removal etch (DRE); wet chemical processing comprised of alkaline and acidic etch followed by modified acidperoxide cleaning and final HF dip. DRE can partially diminish the results of texturization in terms of reflectivity; however, this is a necessary trade-off in solar cell processing to keep a low surface recombination velocity (SRV).

A second dry texturization alternative is a process based on microwave-powered These antennas are positioned antennas. above the substrates, providing sufficient radical density to cause chemical etching on the surface. Ions do not play a role in this process unless a radio frequency (RF) bias is applied. Process gases are SF<sub>6</sub>, N<sub>2</sub>O and Cl<sub>2</sub>. The process is self-masking in that the residues of the etching process are temporarily deposited on the surface. leading to a local etch block and the formation of a texture.

A third dry texturization process for silicon wafers was developed using a remote plasma source chemical downstream etcher, where the plasma is ignited by a microwave source situated above the reaction chamber that allows the ions to be trapped before reaching the wafer. In contrast to RIE, there is no acceleration of ions by a bias voltage. Reactions on the silicon surface are carried out by radicals. Gases used are SF<sub>6</sub> and O<sub>2</sub>. No ensuing wet chemical processing is required.

When plasma texturization is applied as a replacement for wet texturization in standard, thick (e.g., 200 µm) screen-printed solar cells, it yields similar or only slightly higher conversion efficiencies. In practice, the significant benefits of plasma texturization are most likely to be realized with advanced structures, with very thin wafers, and with specialized substrates such as silicon ribbons and epitaxial layers on low-cost silicon substrates. For these specialized substrates, plasma texturization is enabling an technology, as there is no straightforward wet chemical texturization process.

One important issue associated with plasma texturization is gas abatement. While replacing wet texturization by plasma texturization would reduce the amount of wastewater, the release of greenhouse gases could offset the environmental advantage associated with solar panels.  $SF_6$ , for instance, has a huge global warming potential (GWP) of 24,000. Just a few percent of the SF<sub>6</sub> flow getting past the leads abatement system to а poor environmental balance. which is unacceptable for a PV product. This problem is common to several processes in microelectronics and, increasingly, thin-film PVs (e.g., reactor etching). Producers of gas and abatement systems have responded to the challenge and are developing solutions

that can lead to zero release of GWP gas, either by effective recycling of the fluorinated species, or by offering alternative gas systems with low GWP<sup>5</sup>.

discussing the various In trade-offs associated with texturization, it is apparent that there are numerous considerations. Yet, the ultimate requirement is not a technical requirement, but a business necessity. It is critical to consider the trade-offs in processing not simply as a series of technical trade-offs, but as a series of business trade-offs. COO is a tool that can be applied to this analysis, resulting in a disciplined, objective analysis of the technical trade-offs.

Given the number of processes for saw damage removal, texturization and cleaning, a complete COO analysis of each technology along with each configuration is well beyond the scope of this paper. Instead, we have decided to evaluate a configuration for a wet processing sequence that the authors perceive as being commonly used in production today. The remainder of the paper will discuss this process and the associated COO.

#### **Current State of Wet Processing**

In considering a 30 MW line, an analysis was performed to determine the required capacity of the texturization process step. The result was a need to process 1200 wph. The equipment configuration used in the analysis was:

- Preclean: using an alkaline etch to remove saw damage and preclean wafers prior to the texturization step.

- Texturization: using KOH/IPA tanks. Multiple tanks are needed to support the throughput requirements.

• Post-clean using HF/HCl: to remove chemical residues and render the wafer surface nearly metal-free.

#### **Typical Conditions**

A 25 minute process time is achieved with 80 degrees C in each KOH/IPA tank. Bath life is estimated to last for 24 hours with a feed and bleed mechanism. The feed and bleed mechanism allows the addition of small volumes of fresh chemicals and bleed of similar volumes of used chemicals. This helps keep the etch by-products below a maximum threshold. Accumulation of etch by-products will eventual work as an etch mask and heavily contaminate the wafer surface with silicates. The post clean is typically a 1:1:200 HF/HCl/Water at ambient temperature for 5 minutes which achieves a bath life is 5 days.

#### **Future Process Changes**

The PV industry has enjoyed rapid, profitable growth. With increased competition and cost pressures, solar cell manufacturers are competing to produce high efficiency solar cells at the lowest cost possible. Areas of opportunity in the wet processing arena include:

- Chemistry change: efforts have already been made to develop texturization chemistries to replace IPA in the KOH/IPA mixtures<sup>4,6</sup>. Surfactants could replace IPA and provide equally texturized surfaces. In addition, plasma processes have shown promise to replace acidic texturization. However, the issue of gas abatement may offset the environmental advantages of less waste water.

- Automation: further automation can be employed to reduce wafer breakage and minimize/eliminate contamination.

- Statistical Process Control (SPC): recent trends show the need for process control. Equipment manufacturers are now offering sensors and technologies to monitor and control the concentration of chemicals over the bath life. This concentration control accurately predicts the chemical concentration required to produce the desired results. It also enables the extended use of chemicals and, hence, lowers COO and increases process robustness. It will further reduce the installation time and reduce rework and wafer misprocessing.

- Tightened Specifications: this would require more sophisticated techniques for surface conditioning to eliminate foreign contaminants on the wafers. This may mandate that equipment makers build equipment with stringent contamination (e.g., particles, metals) and etch uniformity specifications. This may require including features like minienvironments for the equipment, filtration of chemicals, and high purity materials of construction. This would require solar cell manufacturers to adopt many of the same clean room protocols that are already in use in the integrated circuit (IC) industry.

- Water consumption: just like the IC industry, wet cleans and etch processes use large volumes of water to remove chemicals from the wafer. Cost drivers and environmental pressures will force solar cell manufacturers to find ways to use less water. This could be in the form of using dilute chemicals and thereby needing less rinse water.

#### References

- For a detailed discussion of the history, standards, and algorithms of COO and OEE please see "Cost of Ownership and Overall Equipment Efficiency: A Photovoltaics Perspective," Photovoltaics International, Ed. 6.

- Neuhaus, D-H., and Munzer, A., "Industrial Silicon Wafer Solar Cells", Advances in OptoElectronics, Vol. 2007, Article ID 24521, 15 pages.

- 3. Holdermann, K., "Method for the Wet Chemical Pyramidal Texture Etching of Silicon Surfaces", US patent 6,451,218, Sept. 17, 2002.

- Kashkoush, I., Chen, G., and Nemeth, N., Technical Solar R&D Reports Sept.-Dec. 2009.

- E. Ryabova, "A Review of Solar Wafer Cleaning and Texturing Methods," Photovoltaics World, May/June 2009, 12-15.

- Mayer, K. et al., "New Surfactants for Combined Cleaning and Texturing of Mono-Crystalline Silicon Wafers after Wire-Sawing", Proc. 23<sup>rd</sup> Euro. PVSEC, 1-5 Sept. 2008, Valencia, Spain.

#### Authors

Ismail Kashkoush, Akrion Systems, Allentown, Pennsylvania, USA David W. Jimenez, Wright Williams & Kelly, Inc., Pleasanton, California, USA

### Wright Williams & Kelly, Inc. Conducts 6th Annual Semiconductor Manufacturing Technology Survey

Wright Williams & Kelly, Inc. (WWK), a cost & productivity management software and consulting services company, announced today the start of its 2012 survey on equipment and process timing in the semiconductor industry. The survey results will be consolidated and provided to all participants free of charge. Participation in the survey is the only way to receive a full set of results. The survey form can be downloaded from the WWK Web site at: http://www.wwk.com/2012survey.pdf.

Last year's survey showed that respondents expect to see the following manufacturing technologies in production by 2012:

- Double patterning

- Through Silicon Vias (TSV)

- Through Silicon Vias Cu Fill

- HiK Gate (HfO<sub>2</sub>, ZrO<sub>2</sub>, etc.)

- Equipment suppliers using remote diagnostic capability

- Manufacturing capacity, utilization and cycle time simulation

- Implementation of 300 mm prime advances

However, survey respondents did not expect to see the following technologies in production until 2015 or beyond:

- 193 nm high index immersion lithography

- Direct write

- EUV lithography

- Imprint lithography

With more than 3,000 users worldwide, Wright Williams & Kelly, Inc. is the largest privately held operational cost management software and consulting company serving technology-dependent and technology-driven organizations. WWK maintains long-term relationships with prominent industry resources including SEMATECH, National Institute of Advanced Industrial Science and Technology (AIST), Semiconductor Equipment and Materials International (SEMI), and national labs and universities. Its client base includes nearly all of the top 20 semiconductor manufacturers and equipment and materials suppliers as well as leaders in nanotechnology, micro electro-mechanical systems (MEMS), thin film record heads, magnetic media, flat panel displays (FPD), solid state lighting/light emitting diodes (SSL/LED), and photovoltaics (PV).

#### WWK Hosts Cost of Ownership Seminar at SEMICON West/Intersolar

WWK and SEMI Cosponsor Event for the 20<sup>th</sup> Consecutive Year

Wright Williams & Kelly, Inc. (WWK), the world's preeminent operational cost modeling software and consulting services company, announced today that it will be presenting its highly acclaimed seminar, "Understanding & Using Cost of Ownership," during SEMICON West/Intersolar North America. It will be held at the San Francisco Marriott on Thursday, July 12 from 9am to 5pm. This seminar covers all aspects of cost of ownership (COO) and overall equipment efficiency (OEE) from fundamentals to hands-on applications and has been enhanced to meet the needs of the photovoltaics (PV) industry.

There is limited seating available for this seminar, so please contact Semiconductor Equipment and Materials International (SEMI) today to guarantee your place in this once-a-year event. As an added benefit, WWK's software maintenance clients qualify for a 20% discount off the list price of the seminar if booked directly with WWK.

With more than 3,000 users worldwide, Wright Williams & Kelly, Inc. is the largest privately held operational cost management software and consulting company serving technology-dependent and technology-driven organizations. WWK maintains long-term relationships with prominent industry resources including SEMATECH, National Institute of Advanced Industrial Science and Technology (AIST), Semiconductor Equipment and Materials International (SEMI), and national labs and universities. Its client base includes nearly all of the top 20 semiconductor manufacturers and equipment and materials suppliers as well as leaders in nanotechnology, micro electro-mechanical systems (MEMS), thin film record heads, magnetic media, flat panel displays (FPD), solid state lighting/light emitting diodes (SSL/LED), and photovoltaics (PV).

WWK's product line includes TWO COOL® for detailed process step level COO and OEE, PRO COOL® for process flow and test cell costing, Factory Commander® for full factory capacity analysis and activity based costing, Factory Explorer® for cycle time reduction and work-in-process (WIP) planning, and TCOe<sup>TM</sup> for energy production project costs (cost/kilowatt-hour). Additionally, WWK offers a highly flexible product management software package that helps sales forces eliminate errors in product configuration and quotation processes.

July 10–12, 2012 Moscone Center, San Francisco, California

#### WWK Launches Next Generation of Levelized Cost of Energy (LCOE) Modeling Platform

Wright Williams & Kelly, Inc. (WWK), a cost & productivity management software and consulting services company, announced the introduction of its newest software solution, Total Cost of Ownership for Energy<sup>TM</sup> (TCOe<sup>TM</sup>).

LCOE can be thought of as the price at which energy must be sold to break even over the lifetime of the technology. It yields a net present value in terms of, for example, cents per kilowatt-hour. This is an assessment of the economic lifetime energy cost and lifetime energy production and can be applied to essentially any energy technology. For computing the financial costs the equations can be embellished to take into account not only system costs, but also factors such as financing, insurance, maintenance, and different types of depreciation schedules.

$$LCOE = \frac{PCI - \sum_{n=1}^{N} \frac{DEP + INT}{(1+DR)^n} \times TR + \sum_{n=1}^{N} \frac{LP}{(1+DR)^n} + \sum_{n=1}^{N} \frac{AO}{(1+DR)^n} \times (1-TR) - \frac{RV}{(1+DR)^N}}{\sum_{n=1}^{N} \frac{Initial \ kWh \times (1-SRD)^n}{(1+DR)^n}}$$

Where:

| PCI         | = | Project costs - (investment tax credits or grants)        |

|-------------|---|-----------------------------------------------------------|

| n           | = | Individual years in the project lifetime                  |

| Ν           | = | Lifetime of project in years                              |

| DEP         | = | Depreciation                                              |

| INT         | = | Interest paid                                             |

| TR          | = | Tax rate                                                  |

| DR          | = | Discount rate                                             |

| LP          | = | Loan payment                                              |

| AO          | = | Operating costs                                           |

| RV          | = | Residual value                                            |

| Initial kWh | = | Kilowatt-hours produced by equipment when first installed |

| SDR         | = | Kilowatt-hours degradation rate                           |

|             |   |                                                           |

Given that LCOE was originally designed as a breakeven model, it has limited application to situations where the project owner is interested in revenue (profit) generation or in installations where the electricity produced is displacing some or all of the high cost tier grid supply. For these applications, a new model has been developed called Total Cost of Ownership for Energy<sup>TM</sup> (TCOe<sup>TM</sup>). TCOe<sup>TM</sup> includes additional factors such as revenue/displacement and cost factors applicable to both rooftop and utility scale applications.

By its nature, LCOE is limited in the breadth of questions it can answer and boils down to simply "which energy producing project will generate the lowest kilowatt-hour cost in today's dollars?" TCOe<sup>™</sup> attempts to remove some of the limitations of LCOE with regard to revenue generation, the value of grid power displaced, and the value of power density when faced with space constraints inherent in rooftop installations. However, it is still meant to be a project ranking methodology.

#### **Upcoming "Modeling 101" Paper in Future Photovoltaics**

Future Photovoltaics' upcoming (April 2012) 7<sup>th</sup> edition contains a paper written by Wright Williams & Kelly, Inc. The journal can be obtained at <u>http://www.futurepv.com</u>. The premise of the paper is:

With increased competition and decreased government subsidies, PV manufacturers and project developers are living with increased pressure on operating margins. There is an old adage that says "you can't manage (or fix) what you can't measure." Modeling provides an opportunity to 'measure' the results of changes before incurring the cost of those changes. The alternative is to make the changes and hope the outcome is as expected. Modeling is a forward-looking (predictive) measurement tool versus the alternative of a retrospective review.

For the PV industry, modeling solutions already exist; it is just a matter of management empowering its staff to use these tools to make better business decisions. One of the pitfalls of technical product manufacturing is forgetting that even technical decisions are business decisions. Modeling provides a 'translation' of technical decisions (e.g., throughput, yield, materials consumption) into business results (cost, margin, profit).

The models available today fall into three broad categories: cost of ownership (COO), factory level modeling, and levelized cost of energy (LCOE). The first two are focused on PV manufacturing and assembly and are used by both manufacturers and their suppliers. LCOE is focused on project development, but is impacted by the products produced by PV manufacturers. Which model to use is based on what questions need to be answered. Selecting the right model and modeling methodology is the first step in the successful implementation of this business improvement process.

#### WWK to Present at the Photovoltaics Fab Managers Forum Europe

Wright Williams & Kelly, Inc. has been invited to speak at the upcoming PV Fab Managers Forum to be held March 25-27, 2012 at the Hotel Kempinski Bristol, Berlin, Germany. Information on the event can be found at <u>http://www.pvgroup.org/Events/p040664</u>. WWK will be presenting on March 27 in the session entitled "Total Cost of Ownership in Manufacturing" and will feature information on the use of operational modeling in PV and the entire range of applications from COO through factory level modeling to LCOE/TCOe<sup>TM</sup>.

APPLIED Cost MODELING Winter 2012